商机详情 -

石家庄差分晶振排行榜

差分晶振的电压选择:关键步骤与考虑因素

在选择差分晶振时,电压是一个至关重要的参数。本文将探讨差分晶振电压选择的关键因素和步骤。

1、了解差分晶振的基本特性是必要的。差分晶振的电压范围通常为2.5V至3.3V。这些电压值是通过VDD/SupplyVoltage引脚供电的。在选择电压时,首先要确保电源电压与差分晶振的电压范围相匹配,以避免电压过高或过低导致设备损坏或性能下降。

2、考虑设备的整体需求。不同的设备对电压的要求可能有所不同。例如,某些设备可能需要更高的电压以保证稳定的性能,而另一些设备则可能需要更低的电压以节省能源。因此,在选择差分晶振的电压时,需要综合考虑设备的整体需求。

3、差分晶振的封装体积和工作温度也是影响电压选择的重要因素。封装体积较小的差分晶振可能需要较低的电压以保证稳定的性能,而工作温度较高的设备可能需要更高的电压来确保晶振的稳定运行。

4、需要注意的是,差分晶振的电压选择不仅关系到设备的性能,还可能影响设备的可靠性和寿命。因此,在选择差分晶振的电压时,应充分考虑各种因素,并参考设备制造商的推荐值。

差分晶振的电压选择是一个复杂而关键的过程。通过综合考虑晶振特性的推荐值,可以确保选择到适合的电压。

差分晶振的谐波失真如何?石家庄差分晶振排行榜

差分晶振的精度:揭示其细微之处

差分晶振,作为现代电子设备中不可或缺的一部分,其精度对于确保设备的稳定运行至关重要。那么,差分晶振的精度究竟能达到多高呢?

差分晶振的精度通常用ppm(百万分之一)来表示。ppm值越小,意味着晶振的精度越高。差分晶振的精度范围通常在±25ppm到±100ppm之间。这意味着,差分晶振可以提供非常高精度的时钟信号,特别适用于需要高精度时钟的领域,如数字信号处理、高速数据传输等。

差分晶振的高精度特性主要得益于其差分振荡的方式。这种振荡方式有助于消除晶体振荡器的温度漂移和震荡,从而保证时钟信号的稳定性和精确性。此外,差分晶振还能提供高速的时钟信号,适用于高速数据传输领域,如千兆以太网、USB3.0等。

除了高精度外,差分晶振还具有低电平、低抖动、低功耗、相位低、噪音低、损耗低、精密稳定等特性。这些特性使得差分晶振在电子设备中扮演着至关重要的角色。

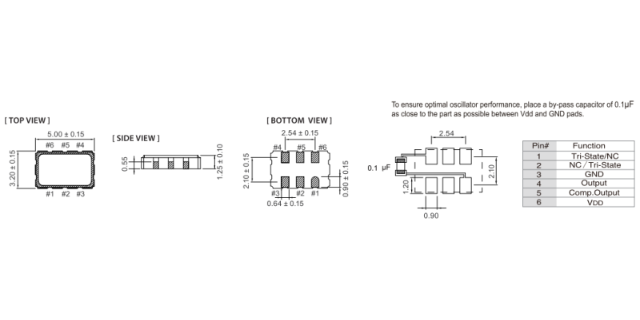

在选择差分晶振时,除了考虑精度外,还需要考虑其封装尺寸、频率范围、输出模式、工作电压和工作温度等因素。这些因素将直接影响差分晶振的性能和使用效果。

总之,差分晶振的高精度特性使其在电子设备中发挥着不可替代的作用。 石家庄差分晶振排行榜差分晶振的负载电容如何选择?

差分晶振的输出波形分析:LVPECL/LVDS/HCSL

差分晶振是一种重要的电子元件,其输出波形主要有正弦波、方波和准正弦波三类。这些波形在电子设备和通信系统中发挥着关键作用。

正弦波型是差分晶振最常见的输出波形之一,具有周期性、连续性和光滑性的特点。正弦波型的频率、振幅和相位可以根据电路设计的需求进行调整,因此,它在通信领域中常用于频率调制和解调、射频处理、无线电发射和接收等关键环节。

方波型是差分晶振另一种常见的输出波形,主要由高电平和低电平两个阶跃函数组成,两者之间的切换非常迅速,具有明显的上升和下降沿。方波型适合数字电路和时序控制等相关应用,如数字系统中的时钟信号、数据采样和信号同步等任务。

准正弦波型则介于正弦波和方波之间,可以是方波形状的圆角梯形波,也可以是更接近正弦波的波形。准正弦波型的应用场景则更为多样,既可以用于模拟信号处理,也可以用于数字通信系统的时钟。

差分晶振的输出波形具有多种特点,如方波的快速切换、低噪声和抖动、良好的对称性等。这些特点使得差分晶振在各种电子设备和通信系统中具有多样的应用。需要注意的是,差分晶振的输出波形和性能还受到电路设计、制造工艺和环境条件等多种因素的影响。

差分晶振的频率稳定性分析

差分晶振具有优良的频率稳定性和低相位噪声特性。

差分晶振的频率稳定性主要得益于其独特的工作原理和结构设计。其内部包含两个相互耦合的振荡器,通过差分信号驱动,有效消除了外部干扰和温度变化对频率的影响。此外,差分晶振的振荡频率通常与石英晶体的固有频率相匹配,这使得其具有较高的频率精度和稳定性。

在实际应用中,差分晶振的频率稳定性受到多种因素的影响。首先,环境温度的变化会对差分晶振的频率产生影响。虽然差分晶振具有较低的温度系数,但仍需在设计时考虑温度补偿措施。其次,电源噪声和电磁干扰也会对差分晶振的频率稳定性造成一定的影响。因此,在选择差分晶振时,应充分考虑其抗干扰能力和电源噪声抑制能力。

为了提高差分晶振的频率稳定性,可以采取以下措施:首先,优化差分晶振的电路设计,降低电源噪声和电磁干扰对频率稳定性的影响;其次,选用高质量的石英晶体作为谐振元件,提高差分晶振的固有频率精度;采用温度补偿技术,减小环境温度变化对差分晶振频率的影响。

差分晶振具有优良的频率稳定性和低相位噪声特性,是电子设备中实现高精度、高稳定度频率源的理想选择。 差分晶振如何与FPGA连接?

差分晶振的驱动电路设计是一项关键的技术任务。差分晶振作为频率源,其驱动电路的设计直接影响到整个系统的性能。

首先,明确差分晶振的规格和参数是驱动电路设计的基础。我们需要了解差分晶振的频率范围、输出波形、功耗、尺寸等参数,以便在设计中充分考虑这些因素。根据应用需求,选择合适的差分晶振,确保其在工作环境中能够稳定输出所需频率。

其次,在驱动电路设计中,要特别注意降低寄生电容和温度的不确定性。晶振应尽量靠近芯片放置,缩短线路长度,防止线路过长导致的串扰和寄生电容。同时,对晶振周围进行包地处理,以减少对其他电路的干扰。

此外,还需考虑负载电容的回流地设计,确保回流路径短且有效。在走线设计时,应遵循一定的规则。例如,晶振底部应避免走信号线,特别是高频时钟线。走线时,应先经过电容再进入晶振,以减少对晶振的影响。对于贴片无源晶振和有源晶振,应根据其封装和引脚类型选择合适的走线方式。

差分晶振的驱动电路设计还需要考虑电源和负载条件。选择合适的电源和负载规格,以确保差分晶振在工作过程中具有足够的稳定性和可靠性。

综上所述,差分晶振的驱动电路设计是一项综合性的技术任务,需要综合考虑多个方面的因素。 133m差分晶振-差分晶振选型,样品报价。云南差分晶振采购

差分晶振的缓冲器如何选择?石家庄差分晶振排行榜

LVDS(LowVoltageDifferentialSignaling,低电压差分信号)接口,又称为RS-644总线接口,是20世纪90年代提出的一种数据传输和接口技术。它克服了TTL电平方式在传输宽带高码率数据时功耗大、电磁干扰大的问题。采用低压和低电流驱动方式,实现了低噪声和低功耗,因此在液晶电视等需要高信号完整性和低抖动的系统中得到了广泛应用。CML(CurrentModeLogic,电流模式逻辑)则是一种常用于网络物理层传输和高速Serdes器件的接口技术。其理论极限速度可达10Gbit/s,功率更低,外部更简单。CML的输出电路形式是一个差分对,输出信号的摆幅与供电电压有关,耦合方式则根据接收器和发送器的电源配置来选择。LVPECL(LowVoltagePositiveEmitter-CoupledLogic,低电压正射极耦合逻辑)接口由ECL和PECL发展而来,使用3.3V电平。其输出结构为一对差分信号,通过电流源接地。LVPECL的差分输出端具有特定的传输阻抗和输出电平,使其在各种应用场景中都能保持稳定的性能。VML(VoltageModeLogic,电压模式逻辑)接口则具有其独特的电压特性和信号传输方式,为不同设备间的连接提供了灵活的选择。这四种接口技术各具特色,为现代电子设备提供了高效、稳定的数据传输方案。石家庄差分晶振排行榜