商机详情 -

陕西差分晶振生产商

差分晶振的自动频率控制(AFC)功能探讨

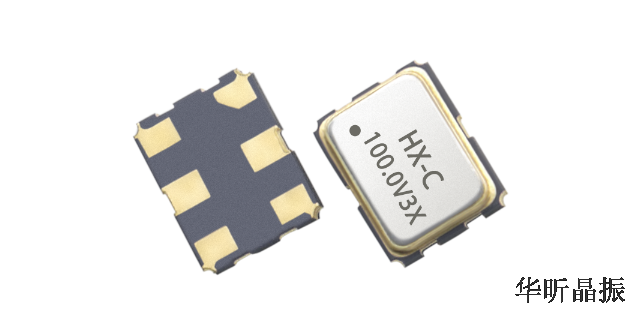

差分晶振经常应用于通信、测量和控制系统等领域。而自动频率控制(AFC)功能,更是差分晶振在实际应用中不可或缺的一部分。AFC功能的主要作用是对差分晶振的输出频率进行自动调整,以保持其准确性和稳定性。在实际应用中,由于环境温度、电源电压等外部因素的影响,晶振的输出频率可能会发生漂移,从而影响整个系统的性能。此时,AFC功能就能够根据频率的偏差,自动调整晶振的控制参数,使其输出频率回到预设的准确值。AFC功能的实现通常依赖于一个闭环控制系统。该系统首先通过频率检测电路对差分晶振的输出频率进行实时监测,然后将实际频率与预设的准确值进行比较,得出频率偏差。接着,控制系统会根据这个偏差,通过调整晶振的控制电压或电流,来改变其输出频率,直到实际频率与预设值一致为止。需要注意的是,AFC功能的实现需要考虑到多种因素,如频率检测的精度、控制系统的稳定性、调整范围的限制等。因此,在实际应用中,需要根据具体的应用场景和需求,对AFC功能进行合理的设计和优化,以确保其能够有效地提高差分晶振的频率稳定性和准确性。总之,差分晶振的自动频率控制(AFC)功能是其在实际应用中不可或缺的一部分 100m差分晶振-差分晶振选型,样品报价。陕西差分晶振生产商

差分晶振的缓冲器选择指南

差分晶振的缓冲器是确保晶振稳定工作的关键组件。在选择差分晶振的缓冲器时,我们需要考虑几个关键因素,以确保其满足应用需求并提供比较好性能。

1、要考虑缓冲器的频率响应。缓冲器需要具有足够的带宽来传递差分晶振产生的振荡信号,同时保持信号的完整性和稳定性。

2、在选择缓冲器时,应确保其具有适当的频率响应范围,以匹配差分晶振的工作频率。其次,要考虑缓冲器的噪声性能。缓冲器引入的噪声可能会对差分晶振的性能产生负面影响。因此,在选择缓冲器时,应评估其噪声水平,并选择具有低噪声性能的缓冲器,以确保差分晶振的稳定性和准确性。

3、还要考虑缓冲器的电源要求。缓冲器通常需要稳定的电源供应,以保持其正常工作。在选择缓冲器时,应确保其电源要求与您的系统电源相匹配,并考虑使用适当的电源滤波和稳定措施,以减少电源噪声对缓冲器性能的影响。

4、要考虑缓冲器的封装和尺寸。根据应用的需求,选择适当的封装和尺寸对于缓冲器的集成和安装至关重要。在选择缓冲器时,应确保其封装和尺寸与您的系统要求相匹配,并考虑其可靠性和可维护性。

选择差分晶振的缓冲器时,需要考虑频率响应、噪声性能、电源要求以及封装和尺寸等因素。 陕西差分晶振生产商差分晶振在低温环境下的性能如何?

差分晶振的驱动电路设计是一项关键的技术任务。差分晶振作为频率源,其驱动电路的设计直接影响到整个系统的性能。

首先,明确差分晶振的规格和参数是驱动电路设计的基础。我们需要了解差分晶振的频率范围、输出波形、功耗、尺寸等参数,以便在设计中充分考虑这些因素。根据应用需求,选择合适的差分晶振,确保其在工作环境中能够稳定输出所需频率。

其次,在驱动电路设计中,要特别注意降低寄生电容和温度的不确定性。晶振应尽量靠近芯片放置,缩短线路长度,防止线路过长导致的串扰和寄生电容。同时,对晶振周围进行包地处理,以减少对其他电路的干扰。

此外,还需考虑负载电容的回流地设计,确保回流路径短且有效。在走线设计时,应遵循一定的规则。例如,晶振底部应避免走信号线,特别是高频时钟线。走线时,应先经过电容再进入晶振,以减少对晶振的影响。对于贴片无源晶振和有源晶振,应根据其封装和引脚类型选择合适的走线方式。

差分晶振的驱动电路设计还需要考虑电源和负载条件。选择合适的电源和负载规格,以确保差分晶振在工作过程中具有足够的稳定性和可靠性。

综上所述,差分晶振的驱动电路设计是一项综合性的技术任务,需要综合考虑多个方面的因素。

差分晶振的谐波失真探讨

差分晶振,谐波失真作为评价差分晶振性能的重要指标之一,其表现情况受到多样关注。首先,我们需要了解谐波失真的基本概念。在理想情况下,差分晶振的输出信号应该与输入信号保持一致,但由于电子设备的非线性特性,输出信号往往会发生形状变化,导致谐波成分增多,从而引起谐波失真。这种失真会使得输出信号的波形发生畸变,进而影响到信号的准确性和稳定性。差分晶振作为一种高精度、高稳定性的振荡器,其谐波失真情况通常被控制在较低的水平。然而,在实际应用中,由于各种因素的影响,如温度变化、电源电压波动等,差分晶振的谐波失真可能会发生变化。因此,对于差分晶振的设计和制造,需要充分考虑这些因素,并采取有效的措施来降低谐波失真。此外,对于差分晶振的使用者而言,了解并掌握差分晶振的谐波失真特性也是非常重要的。通过合理的电路设计和优化,可以进一步降低差分晶振的谐波失真,提高系统的整体性能。总的来说,差分晶振的谐波失真情况是一个复杂而重要的问题。

在实际应用中,我们需要通过不断的研究和实践,探索更加有效的降低谐波失真的方法,以提高差分晶振的性能和稳定性,为现代电子设备的发展提供有力的支持。 差分晶振的调谐精度如何?

差分晶振的振动模式解析差分晶振,作为高速数据传输的关键组件,其振动模式对于系统的性能起着至关重要的作用。在众多的差分晶振中,主要存在以下几种振动模式。

LVDS(LowVoltageDifferentialSignaling)模式是一种常见的差分晶振振动模式。这种模式下,信号以低电压的差分形式传输,既降低了功耗,又提高了信号的抗干扰能力。它广泛应用于各种高速数据传输场合。

LVPECL(LowVoltagePositiveEmitterCoupledLogic)模式则是另一种重要的差分晶振振动模式。其信号的摆幅较高,功耗大于LVDS,但驱动能力更强,适用于10Gbps的高速数据传输。

CML(CurrentModeLogic)模式则是靠电流驱动,其输入和输出匹配良好,使用时直接连接即可,是高速数据接口形式中简单的一种。如XAUI、10GXFI接口均采用CML电平。

此外,差分晶振的振动模式还受到其性能参数的影响,如频率范围、相位噪声、温度稳定性、功耗以及输出幅度等。这些因素共同决定了差分晶振在不同应用中的振动模式选择。

总结来说,差分晶振的振动模式主要有LVDS、LVPECL和CML等,每种模式都有其独特的优点和适用场景。在选择差分晶振时,需要根据具体的应用需求,综合考虑其性能参数和振动模式,以实现合适的系统性能。 差分晶振的同步能力如何?陕西差分晶振生产商

差分晶振的滤波器如何选择?陕西差分晶振生产商

差分晶振作为一种高精度、高稳定度的频率源,在现代电子设备中发挥着至关重要的作用。然而,任何晶振都无法完全避免相位抖动的存在,差分晶振也不例外。相位抖动是衡量晶振性能的重要指标之一,它直接关系到输出信号的稳定性和可靠性。

差分晶振的相位抖动主要来源于内部电路噪声、外部环境干扰以及温度变化等因素。内部电路噪声是不可避免的,但可以通过优化电路设计、选用低噪声器件等方式来降低其影响。外部环境干扰,如电磁辐射、机械振动等,也可能对差分晶振的相位稳定性产生负面影响。此外,温度变化也是导致相位抖动的重要因素,因为晶振的频率随温度变化而发生漂移。

为了降低差分晶振的相位抖动,制造商通常会采用一系列技术手段。例如,采用温度补偿技术来减小温度变化对频率稳定性的影响;使用低噪声放大器和滤波器来降低内部电路噪声;以及采用屏蔽和隔离措施来减少外部环境干扰。这些措施能够显著提高差分晶振的相位稳定性,使其在各种应用场合中都能表现出优异的性能。

总的来说,差分晶振的相位抖动是一个复杂的问题,涉及多个方面的因素。尽管无法完全消除相位抖动,但通过优化设计和采用先进技术,可以将其控制在较小的范围内,从而满足大多数应用的需求。 陕西差分晶振生产商