商机详情 -

时钟有源晶振32MHZ

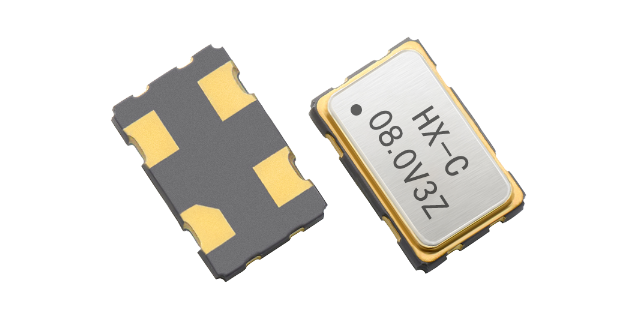

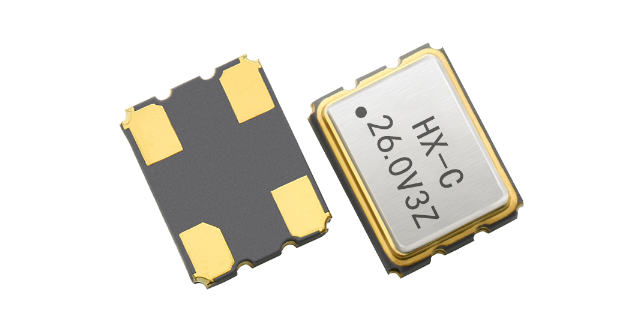

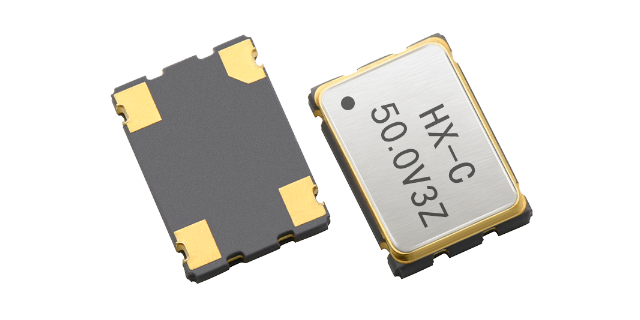

4MHz有源晶振OSC7050:规格参数详解。4MHz有源晶振OSC7050,正是一款广泛应用于各类电子设备中的高质量晶振。

一、基本频率OSC7050的关键特性在于其稳定的4MHz振荡频率。这一频率决定了晶振的基础工作速度,为电子设备的正常运行提供了坚实的基石。

二、输出负载输出负载(OUTPUTLOAD)是晶振规格中极为关键的一项参数。对于OSC7050而言,其输出负载为50pF。这意味着在正常工作状态下,晶振的输出端所连接的电路或器件的等效电容应为50pF,以保证晶振的稳定性和性能优化。

三、性能特点稳定性:OSC7050采用了先进的生产工艺和严格的品质控制,确保了其频率输出的高度稳定性。

低功耗:在保证性能的同时,OSC7050还实现了低功耗设计,适用于对能耗有严格要求的应用场景。

长寿命:得益于好的材料和精湛的工艺,OSC7050具有较长的使用寿命,减少了用户的维护成本。

四、应用场景由于4MHz有源晶振OSC7050具有上述诸多优点,它广泛应用于通信、计算机、仪表、消费电子等多个领域。

在这些领域中,OSC7050为设备提供了稳定、可靠的时钟源,保障了设备的正常运行。 关于有源晶振和无源晶振接MCU的方法。时钟有源晶振32MHZ

有源晶振ST脚不用时的处理方式。ST脚作为有源晶振的一个引脚,其用途和处理方式常常为人们所关注。那么,当有源晶振的ST脚不使用时,是否可以悬空呢?答案是肯定的。首先,我们需要了解有源晶振的基本工作原理。有源晶振通过内部的振荡电路产生稳定的频率输出,而ST脚通常用于设置或调整振荡的频率或相位。然而,在某些应用场景中,我们可能并不需要调整这些参数,因此ST脚就无需连接任何外部设备。在这种情况下,将ST脚悬空是一种可行的做法。悬空意味着ST脚既不连接电源也不连接地线,也不连接其他任何信号线。这样做的好处是可以避免不必要的电气干扰和信号噪声,从而保持有源晶振的稳定性和准确性。当然,悬空ST脚也需要注意一些事项。首先,确保其他引脚正确连接,以保证有源晶振能够正常工作。其次,悬空引脚可能会受到静电或外部电磁场的影响,因此在实际应用中,应当避免将悬空引脚暴露在可能产生静电或电磁场的环境中。综上所述,当有源晶振的ST脚不使用时,可以将其悬空。这种做法既简单又有效,有助于保持有源晶振的稳定性和可靠性。但在实际应用中,仍需注意其他引脚的连接情况和避免静电或电磁场的干扰。时钟有源晶振32MHZ有源晶振使能脚O/E与待机脚Stand-by的功能差异。

有源晶振的相位抖动与相位噪音解析。有源晶振对于保证系统稳定性和准确性起着至关重要的作用。其中,相位抖动和相位噪音是有源晶振的两个关键参数,直接影响了系统的性能。相位抖动,简单来说,就是晶振输出信号的相位在短时间内的随机变化。这种变化可能会导致数据传输的不稳定、通信中断或系统性能下降。相位抖动的产生与多种因素有关,如电源噪声、环境温度变化、机械振动等。因此,在选择有源晶振时,需要考虑其相位抖动的性能指标,以确保系统运行的稳定性。而相位噪音,则是一种更为细致的描述,它反映了晶振输出信号在频率域上的不稳定性。相位噪音通常以分贝为单位,描述了信号在某一频率偏移处的功率与载波功率之比。相位噪音的大小直接影响了系统的信号质量,尤其是在对信号精度要求较高的应用中,如卫星通信、雷达系统等。为了降低相位抖动和相位噪音,可以采取多种措施,如优化电路设计、提高电源稳定性、采用精密封装技术等。此外,随着科技的进步,新型材料和工艺的应用也为有源晶振的性能提升提供了更多可能。

在实际应用中,需要综合考虑各种因素,选择适合的有源晶振,并采取有效措施降低相位抖动和相位噪音,以确保系统的稳定运行和信号质量。

有源晶振的功耗(currentconsumption)是一个重要的性能指标,它决定了晶振在工作状态下所消耗的电流大小。功耗的大小不仅关系到设备的整体能耗,还直接影响到设备的稳定性和可靠性。一般来说,有源晶振的功耗取决于其内部电路设计和制造工艺。不同的晶振型号、不同的工作频率和不同的工作条件,其功耗也会有所不同。在正常工作条件下,有源晶振的功耗通常在几毫安(mA)到几十毫安(mA)之间。为了降低有源晶振的功耗,可以采取一些措施。首先,优化晶振的内部电路设计,减少不必要的功耗。其次,选择低功耗的材料和制造工艺,降低晶振的整体能耗。此外,合理的工作条件和工作频率也能够有效地降低功耗。在实际应用中,需要根据具体的应用场景和需求来选择合适的有源晶振。例如,在一些需要长时间运行的嵌入式系统中,选择低功耗的有源晶振可以明显延长设备的续航时间。而在一些对稳定性要求较高的应用中,需要选择功耗较高但性能更稳定的有源晶振。总之,有源晶振的功耗是一个重要的性能指标,需要根据具体应用场景和需求来选择合适的晶振型号和工作条件。同时,采取一些有效的措施也可以有效地降低有源晶振的功耗,提高设备的整体性能和稳定性。有源晶振规格书中的VDD引脚是什么意思?

常用有源32.768K贴片晶振封装尺寸介绍有源32.768K贴片晶振,经常应用于计时、通信、控制等领域。其封装尺寸的选择对于电路板的布局、整机的性能和可靠性都有着至关重要的影响。常见的有源32.768K贴片晶振封装尺寸有2.5×2.0mm、3.2×2.5mm和5.0×3.2mm等几种。这些尺寸都是根据晶振的频率稳定性、功耗、温度特性等因素综合考虑而确定的。其中,2.5×2.0mm的封装尺寸较小,适合对空间要求严格的电路板设计,如智能手表、微型传感器等。这种尺寸的晶振具有体积小、重量轻的特点,但其频率稳定性和温度特性可能相对较弱。2×2.5mm的封装尺寸在性能和空间占用之间达到了较好的平衡,广泛应用于手机、平板电脑等消费电子产品中。这种尺寸的晶振既保证了频率的稳定性,又适应了大多数电路板的布局要求。而5.0×3.2mm的封装尺寸则更多地应用于工业控制、仪器仪表等需要更高稳定性和可靠性的场合。其较大的尺寸使得晶振内部的电路和结构更加稳定,从而保证了更高的频率精度和温度稳定性。在选择有源32.768K贴片晶振的封装尺寸时,需要根据具体的应用场景和电路板设计进行综合考虑。除了封装尺寸外,还需要关注晶振的频率精度、温度特性、功耗等参数,以确保整机的性能和可靠性。关于有源晶振Overall Frequency Stability/总频差。时钟有源晶振32MHZ

有源晶振三态功能如何使输出引脚(三号脚)处于高阻抗状态?时钟有源晶振32MHZ

有源晶振的总频差(OverallFrequencyStability)分析有源晶振,作为现代电子设备中的关键组件,其性能对系统的稳定性和准确性起着至关重要的作用。其中,总频差(OverallFrequencyStability)是衡量有源晶振性能的重要指标之一。总频差,简单来说,是指晶振在工作过程中,其输出频率与标称频率之间的偏差。这种偏差可能由多种因素造成,如温度变化、电源电压波动、机械振动等。因此,有源晶振的总频差是一个综合反映其在各种环境条件下的性能稳定性的指标。在实际应用中,总频差的大小直接影响到电子设备的性能。例如,在通信系统中,如果晶振的总频差过大,可能会导致信号失真、传输错误等问题,从而影响通信质量。因此,对于需要高精度和高稳定性的应用场合,选择具有优异总频差性能的有源晶振至关重要。为了降低有源晶振的总频差,制造商通常会采用一系列技术手段,如优化电路设计、提高材料质量、加强环境适应性等。同时,用户在使用有源晶振时,也应注意其工作环境和使用条件,以确保其性能得到充分发挥。总之,有源晶振的总频差是衡量其性能稳定性的重要指标。对于追求高精度和高稳定性的电子设备而言,了解和掌握有源晶振的总频差特性,对于确保系统性能具有重要意义。时钟有源晶振32MHZ