商机详情 -

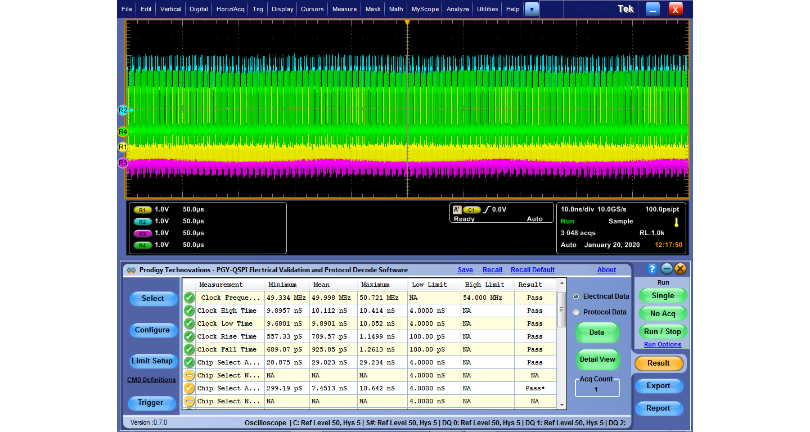

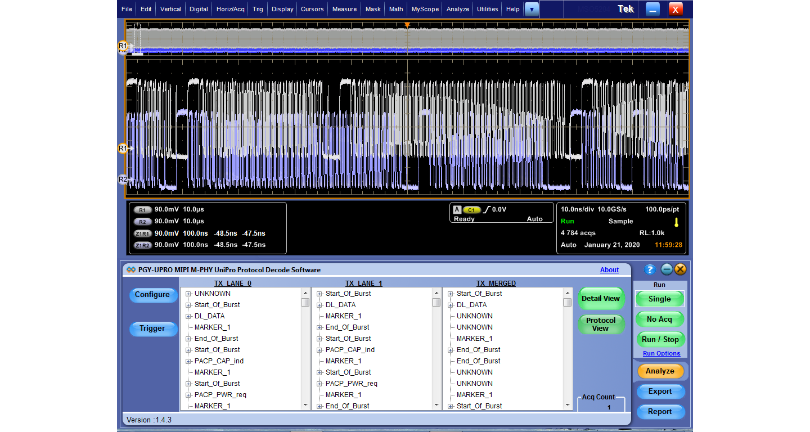

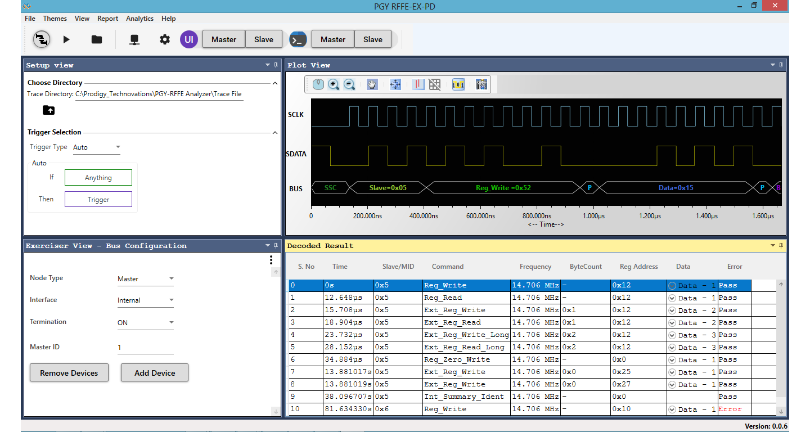

江门PCIE分析仪

每个采样点都只使用一个存储位置。因此,精度越高(采样频率越高),采样周期越短。触发定时分析仪:在测量中的某些点,逻辑分析仪必须了解何时采集(存储)流经其内存的数据。这些点叫做触发点。使分析仪触发的一种方法是:相应地配置分析仪,使之从一组信号(总线)中查找上限或下限码型,或者查找单个信号的上升或下降时钟沿。当分析仪在数据中发现指定的码型或时钟沿时,它便触发。码型触发:码型触发用于在总线上查找特定的上限和下限码型。您可以指定不同的标准,如等于、不等于、在或不在某个范围内或者于/小于。示例:拥有一条包含8条信号线的总线。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro。UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。I2C/SPI协议分析仪/训练器找欧奥!江门PCIE分析仪

影响逻辑分析仪的正常使用的问题。针对上述提出的问题,在原有的逻辑分析仪基础上进行创新设计。技术实现要素:解决的技术问题针对现有技术的不足,本实用新型提供了一种便于散热通风的逻辑分析仪,解决了现有的部分逻辑分析仪常放置于机房内或工作室内,且逻辑分析仪处于相对封闭的状态,使得逻辑分析仪内部的组件在工作中产生的热量无法很好地排出,导致逻辑分析仪内部温度较高,影响逻辑分析仪的正常使用的问题。技术方案为实现上述目的,本实用新型提供如下技术方案:一种便于散热通风的逻辑分析仪,包括逻辑分析仪本体欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。东莞I2C/SPI分析仪费用UFS协议分析仪/训练器找欧奥!

没有额外的被测设备)的一小段时间内,可以自动:定位每个通道上的建立/保持窗口。针对尽可能宽的数据有效窗口调整阈电压设置。眼定位是获得尽可能小的逻辑分析仪建立/保持窗口的一种简单方法。眼定位概要:对于指定的状态采样时钟,眼定位可在时钟沿前后的一个固定时间范围内查找数据信号转变(阈电压交叉点),并为显示相关内容以帮助设置佳采样位置。为了了解眼定位显示,需为每个活动时钟沿拍摄一张有关该时钟沿的数据信号转变的“照片”。将此照片看作快照、定格画面或频闪观测仪(位于时钟沿中心或与时钟沿同步)。到达时钟沿的时间为T=0。例如,如果选择盒1上时钟输入的上升沿作为状态采样时钟,每次拍摄“照片”时,都将达到盒1时钟上的上升沿。盒1时钟沿之间的时间是否相同无关紧要。如果同时在上升沿和下降沿上进行采样,那么在每一个时钟沿上都会拍摄一张“照片”。此外,在活动沿之间消耗了多少时间也不重要。每一个时钟沿上都要拍摄“照片”。要构建眼定位显示,需要将无数张这样的“照片”堆叠在彼此的顶端。每张“照片”都在T=0时对齐,此时将达到活动时钟沿。照片拍自上升沿还是下降沿并没有关系;它们会在T=0时对齐。构建显示后。

序列的每个步骤被称为一个序列步骤。每个序列步骤由两部分组成:条件和操作。条件是指布尔逻辑表达式,例如“IfADDR=1000”或“IfthereisarisingedgeonSIG1”。操作是指符合条件时逻辑分析仪应当执行的内容。操作的示例包括触发逻辑分析仪、转至另一序列步骤以及启动定时器。这类似于编程中的If/Then语句。触发序列中的每个步骤都被指定一个数字。执行的个序列步骤总是序列步骤1,但由于“转到”操作,剩余的序列步骤可以以任意顺序执行。执行一个序列步骤且布尔逻辑表达式均为假时,逻辑分析仪将采集下一样本并再次执行同一序列步骤于“KeepacquiringmoresamplesuntilDATA=7000,thentrigger”。如果符合一个序列步骤中的布尔逻辑表达式,那么在执行下一序列步骤之前总是采集另一样本。换句话说,如果一个样本符合序列步骤1的条件,在执行序列步骤2前将采集另一样本。这意味着一个单独的样本不可能符合多个序列步骤的条中的条件二者之间采集了新的样本,因此逻辑分析仪不会在采集样本#1时触发。可将此触发序列看作是“FindADDR=1000followedbyDATA=2000andthentrigger”。触发序列中的多序列步骤暗示了“后接”。逻辑分析仪触发后,将不会再次触发。换句话说。PCle Gen 4协议分析仪/训练器找欧奥!

这八个触发器都连接到同一时钟信号。图9接收器当时钟线上出现高电平时,所有这八个触发器都会在其“D”输入处采集数据。此外,每次时钟线上出现正电平时都会发生有效状态。下面的简单触发指示分析仪在时钟线上出现高电平时在D0-D7这几条上收集数据。图10总线收集的数据高级触发示例:假设想查看地址值为406F6时内存中存储了哪些数据。对高级触发进行配置,以在地址总线上查找码型406F6(十六进制)以及在RD(内存读取)时钟线上查找高电平。图11高级触发设置在配置EdgeAndPatterntrigger(时钟沿和码型触发)对话框时。尝试将该操作看作是构造从左向右读取的句子。Pod、通道和时间标签存储Pod和通道的命名约定:Pod是一组逻辑分析仪通道的组合,共有17个通道,其中数据16个通道,时钟1个通道。逻辑分析仪的通道数是Pod数的倍数关系。34通道的逻辑分析仪对应两个Pod,68通道逻辑分析仪对应4个Pod,136通道逻辑分析仪对应8个Pod。对于模块化的逻辑分析仪。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪。PCIE协议分析仪/训练器找欧奥!嘉兴逻辑分析仪厂家

协议分析仪就找欧奥电子。江门PCIE分析仪

而在另一端落下。换句话说,由于逻辑分析仪内存的深度(样本数量)有限,因此每当采集新样本时,如果内存已满,将会删除内存中现有的旧的样本。如下图所示。图20逻辑分析仪触发的传送带类比逻辑分析仪触发就像是放置在传送带(上面放置有多个箱子)起始位置上的箱子一样。它们的任务是“查找特殊的箱子,并在该箱子到达传送带的某一特定位置时停止运行传送带”。在此类比中,特殊的箱子就是触发。逻辑分析仪检测到与触发条件相匹配的样本后,就表示当触发位于内存中的适当位置时应停止继续采集样本。触发在内存中的位置被称为触发位置。通常,触发位置被设置在中间,以便使触发前后出现的样本的数量不超出内存范围。不过,也可以将触发位置设置在内存中的任意位置。由于逻辑分析仪触发提供了量功能,因此下表将对本文中介绍的功能进行简要概述。该表将对这些功能进行逐一描述。表1逻辑分析仪触发功能摘要触发序列:虽然逻辑分析仪触发通常很简单,但它们却需要复杂的程序。例如,可能想在某一信号的上升沿后跟另一信号的上升沿时触发。这意味着逻辑分析器必须在开始寻找下一个上升沿之前找到个上升沿。由于拥有一个可查找触发的步骤序列,因此它被称为触发序列。江门PCIE分析仪