商机详情 -

深圳UFS分析仪售价

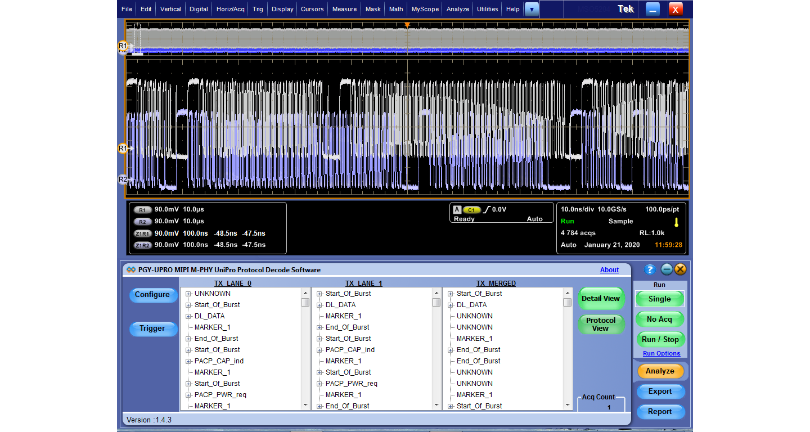

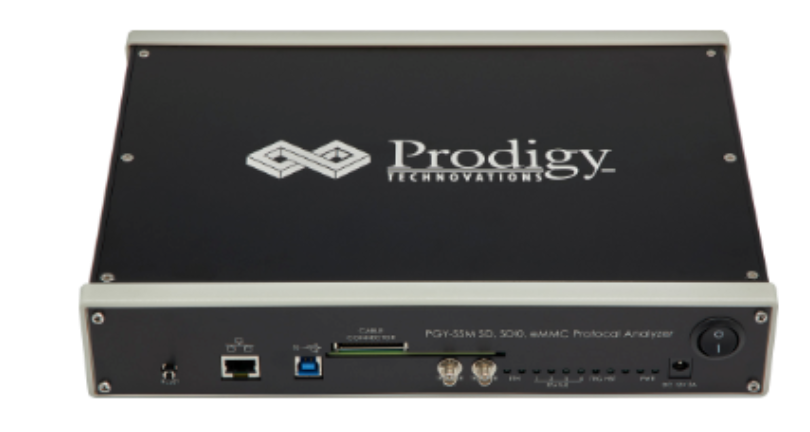

影响逻辑分析仪的正常使用的问题。针对上述提出的问题,在原有的逻辑分析仪基础上进行创新设计。技术实现要素:解决的技术问题针对现有技术的不足,本实用新型提供了一种便于散热通风的逻辑分析仪,解决了现有的部分逻辑分析仪常放置于机房内或工作室内,且逻辑分析仪处于相对封闭的状态,使得逻辑分析仪内部的组件在工作中产生的热量无法很好地排出,导致逻辑分析仪内部温度较高,影响逻辑分析仪的正常使用的问题。技术方案为实现上述目的,本实用新型提供如下技术方案:一种便于散热通风的逻辑分析仪,包括逻辑分析仪本体欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。UniPro协议分析仪/训练器找欧奥!深圳UFS分析仪售价

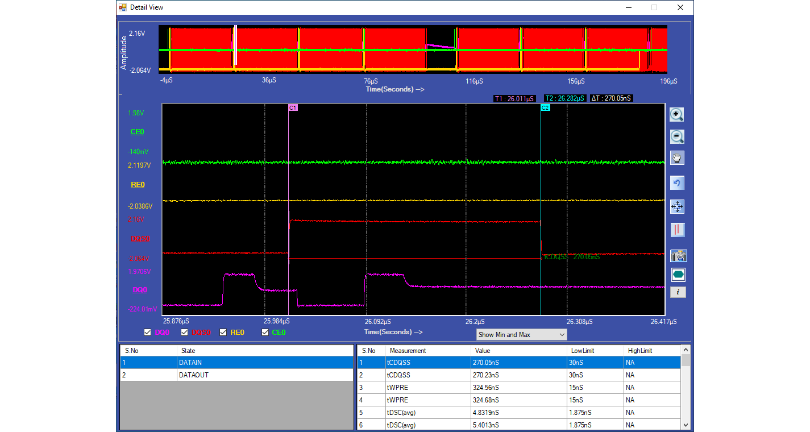

简单触发示例:请看下面显示的“D”触发器,在正值的时钟沿出现之前,“D”输入上的数据是无效的。因此,时钟输入为上限时,触发器的状态才有效。图8D触发器现在,假设我们有并行的八个此类触发器。如下所示,这八个触发器都连接到同一时钟信号。图9接收器当时钟线上出现高电平时,所有这八个触发器都会在其“D”输入处采集数据。此外,每次时钟线上出现正电平时都会发生有效状态。下面的简单触发指示分析仪在时钟线上出现高电平时在D0-D7这几条上收集数据。图10总线收集的数据高级触发示例:假设想查看地址值为406F6时内存中存储了哪些数据。对高级触发进行配置,以在地址总线上查找码型406F6(十六进制)以及在RD(内存读取)时钟线上查找高电平。图11高级触发设置在配置EdgeAndPatterntrigger(时钟沿和码型触发)对话框时,尝试将该操作看作是构造从左向右读取的句子。Pod、通道和时间标签存储Pod和通道的命名约定:Pod是一组逻辑分析仪通道的组合,共有17个通道,其中数据16个通道,时钟1个通道。逻辑分析仪的通道数是Pod数的倍数关系。34通道的逻辑分析仪对应两个Pod,68通道逻辑分析仪对应4个Pod,136通道逻辑分析仪对应8个Pod。对于模块化的逻辑分析仪。阳江EMMC分析仪找哪家UFS协议分析仪/训练器找欧奥!

才能解决速度不够和通道数量不足的问题。图2图3图4下面就以Saleae逻辑分析仪为例,通过采样分析I2C总线波形和PWM波形,简单介绍它的特点和使用方法。先介绍用逻辑分析仪采样单片机对I2C器件AT24C16的写数据过程。硬件连接1.先将逻辑分析仪的GND与目标板的GND连接,让二者共地。2.选择需要采样的信号,这里就是AT24C16的SDA和SCL,将SDA接入逻辑分析仪的通道1(Input1),SCL接入通道1(Input2)。3.将逻辑分析仪和电脑USB口连接,windows会识别该设备,并在屏幕右下角显示USB设备标识。软件使用1.运行Saleae软件,此时逻辑分析仪的硬件已经与电脑相连,软件会显示[Connected]。2.设置采样数量和速度,I2C为低速通信,所以速度设置不必太高,这里设置为20MSamples@4MHz的速度,也就是能持续采样5秒钟。3.设置协议,点右上角的“Options”按钮,找到analyzer1,设置为I2C协议,详见图1。4.按“Start”按钮,开始采样。图5图6数据分析采样结束后,可以看到波形,见图2。由于我们设置了是I2C分析,因此不光显示出波形,还有根据I2C协议解码显示的字节内容。单片机对AT24C16进行写入操作,在0x00地址处写入10000等数字。波形起始是“start”信号,然后依次是AT24C16的标识0xA2。

逻辑分析仪也是必不可少的。逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,主要的作用在于时序判定。逻辑分析仪与示波器不同,它不能显示连续的模拟量波形,而只显示高低两种电平状态(逻辑1和0)。在设置了参考电压后,逻辑分析仪将采集到的信号与电压比较器比较,高于参考电压的为逻辑1,低于参考电压的为逻辑0。这样就可以将被测信号以时间顺序显示为连续的高低电平波形,便于使用者进行分析和调试。使用逻辑分析仪,可以方便地设置信号触发条件开始采样,分析多路信号的时序,捕获信号的干扰毛刺,也可以按照规则对电平序列进行解码,完成通信协议分析。图1逻辑分析仪根据其硬件设备的功能和复杂程度,主要分为式(单机型)逻辑分析仪和基于电脑(PC-Base)的虚拟逻辑分析仪两大类。式逻辑分析仪是将所有的软件,硬件整合在一台仪器中,使用方便。虚拟逻辑分析仪则需要结合电脑使用,利用PC强大的计算和显示功能,完成数据处理和显示等工作。专业逻辑分析仪,通常具有数量众多的采样通道,超快的采样速度和大容量的存储深度,但昂贵的价格也不是个人所能承受的。作为工程师手头常备的开发工具,目前有许多入门级的逻辑分析仪设计。HDMI,MHL协议分析仪/训练器找欧奥!

将内存深度设置为值的一半(或更小)将返回Pod。在状态采样模式中,在选择了高速状态模式采样选项的情况下,会将一个Pod对保留用于时间标签存储。在定时采样模式中,在选择了跳变/存储限定定时模式采样选项的情况下:选择了小采样周期时,会将一个Pod对保留用于时间标签存储。选择了除小采样周期之外的采样周期时,选择采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下,将内存深度设置为值的一半(或更小)将返回Pod。该模块是已分离的逻辑分析仪的一部分。在这种情况下,Pod位于分离分析仪的另一半模块中。状态模式和跳变定时模式下通道数、内存深度和触发之间的相互影响:状态采样模式时,时间标签存储需要1个Pod或1/2的采集内存。在操作界面应用程序中,所有模块都与时间相关;不能关闭timetagstorage(时间标签存储)(虽然以前的Agilent逻辑分析系统可以)。要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。默认设置:时间标签存储始终处于开启状态(并且不能将其关闭)。分析仪哪里买?找欧奥!深圳UFS分析仪售价

JTAG协议分析仪/训练器找欧奥!深圳UFS分析仪售价

触发)操作离开此序列步骤之前,应用该存储限定。如果要为每个序列步骤应用不同的存储限定,该存储限定很有用。例如,可能不希望在ADDR=1000之前存储任何样本,而对于其余的测量,只存储ADDR在1000到2000范围之内的样本。设置序列步骤存储还需要再使用一条分支指令。例如,在查找DATA=005E时,如果只希望存储ADDR在5000到6FFF范围之内的样本,某些情况下可使用以下序列步骤:。这表示“立即存储内存中新获得的样本”。而不表示“从现在起,开始存储”。应当注意,因为当ADDR不在5000到6FFF范围之内时从不执行存储样本操作,所以该分支指令实质上是指“在此序列步骤中,只存储ADDR在5000到6FFF范围之内的样本”。上述示例似乎说明将只存储ADDR在5000到6FFF范围之内的样本。但是,这取决于默认存储的设置方式。还是使用上述示例,如果默认存储设置为“StoreEverything”(存储所有样本)并且有一个样本不在5000到6FFF的范围之内,则不会执行ElseIf分支指令,而应用该“默认存储”。实际上,该序列步骤说明了样本值在特定范围内时要执行的操作,但没有说明样本值在此范围之外时应执行的操作。因此,如果要明确指定序列步骤存储,请使用以下指令:SampleGoto1总之。深圳UFS分析仪售价