商机详情 -

iqd晶振

晶振的抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。抖动可以细分为确定性抖动和随机抖动两种类型。确定性抖动在幅度上是有界的,可预测,它可能在信号上升和下降时导致数据幅度不规则,逻辑电平可能会不规则。而随机抖动则是无界的,不可预测,通常由热噪声引起,如果幅度足够大,会导致随机时序误差或抖动。抖动对电路的影响主要表现在以下几个方面:数据传输质量:抖动可能导致数据传输中的时序误差,影响数据的正确接收和解码,降低通信质量。显示器性能:在显示器应用中,抖动可能导致屏幕闪烁,影响用户的视觉体验。处理器性能:抖动还可能影响处理器的性能,导致处理器在处理数据时产生误差,降低整体性能。为了降低抖动对电路的影响,需要选择高质量的晶振,优化电路设计,减少噪声干扰,并采取适当的抖动补偿措施。同时,根据具体的应用场景,选择可接受的抖动值也是非常重要的。晶振型号齐全,全品类。iqd晶振

晶振的抗干扰能力是其性能评估中的一个重要指标。通常情况下,晶振具有较强的抗干扰能力,这主要得益于其设计和制造过程中的一系列优化措施。首先,晶振的抗干扰能力与其内部结构和材料密切相关。高质量的晶振采用质量的晶体材料和先进的制造工艺,确保其在工作时能够抵抗来自外部环境的干扰,如电磁干扰、温度变化等。其次,晶振的抗干扰能力还受到其封装形式的影响。一些先进的封装技术,如金属封装和陶瓷封装,能够有效地屏蔽外部电磁干扰,提高晶振的抗干扰能力。此外,晶振的抗干扰能力还与其工作频率和工作温度范围有关。一般来说,较低频率的晶振抗干扰能力较强,而高温环境可能会对晶振的性能产生影响,因此在选择晶振时需要根据实际应用环境进行综合考虑。为了提高晶振的抗干扰能力,制造商通常会采取一系列措施,如优化电路设计、加强封装等。同时,用户在使用晶振时也可以采取一些措施来降低干扰的影响,如合理布局电路、选择适当的电源和接地方式等。总之,晶振的抗干扰能力是其性能的重要组成部分,用户在选择和使用晶振时需要关注其抗干扰能力,并根据实际需求进行综合考虑。晶振器晶振的并联电阻和串联电阻对电路有何影响?

为了延长晶振的使用寿命,可以采取以下方法和措施:

温度控制:确保晶振的使用环境温度在合适的范围内,-40°C到85°C是比较理想的温度范围。过高或过低的温度都会对晶振的寿命产生不良影响。

减少振动:在运输、安装和使用过程中,要尽量避免晶振受到振动或冲击。这可以通过适当的包装、固定和隔离措施来实现。

电压控制:根据晶振的电气特性选择合适的电压,避免过高或过低的电压对晶振造成损害。在使用过程中,应定期检查电源电压的稳定性,并确保晶振的输入电压在允许的范围内。

清洁和保养:定期清洁晶振及其周围环境,避免灰尘、油污等污染物对晶振的影响。同时,定期对晶振进行保养和检查,及时发现问题并进行处理。

选择合适的晶振:根据应用需求选择合适的晶振。如果需要宽温度范围工作,可以选择能够在更宽温度范围内稳定工作的晶振。如果需要更高的频率稳定性,可以选择Q值更高的晶振。

防止静电干扰:在运输、安装和使用过程中,要注意避免静电干扰,避免晶振片遭受静电击击破坏。

保持良好的使用环境:尽量避免在潮湿、腐蚀、腐蚀性气体等恶劣环境下使用晶振片。

应选择合适的匹配电容,以确保电路的稳定性和晶振的正常工作。

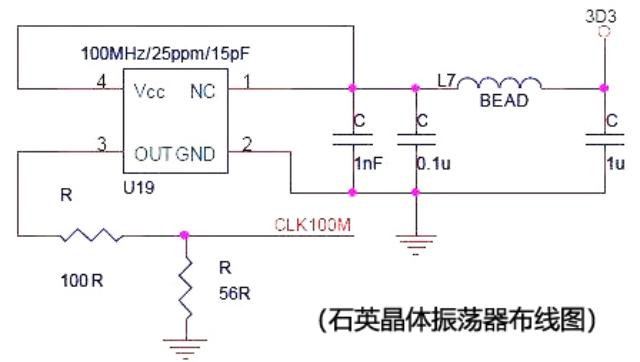

晶振的负载电容是指在电路中跨接晶体两端的总的外界有效电容,这是晶振要正常震荡所需要的电容。它的大小主要影响负载谐振频率和等效负载谐振电阻。负载电容的确定一般依赖于晶振的数据手册或规格书,其中会明确标注出所需的负载电容值。此外,也可以通过计算公式来确定负载电容,公式为:晶振的负载电容Cf=[Cd*Cg/(Cd+Cg)]+Cic+△C,其中Cd、Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C(PCB上电容)经验值为3至5pf。但需要注意的是,不同的IC和PCB材质可能会有所不同,因此需要根据实际情况适当调整。在应用中,一般外接电容是为了使晶振两端的等效电容等于或接近负载电容。如果负载电容不够准确,那么晶振的准确度就会受到影响。因此,在确定负载电容时,需要参考晶振的规格书或数据手册,并结合实际情况进行调整,以确保晶振的稳定性和准确度。晶振与其他类型的振荡器(如RC振荡器)相比有何优势?

提高晶振的精度和稳定性主要可以从以下几个方面着手:优化制造工艺:通过改进制造过程中的切割、清洗、镀膜等步骤,减少制造公差,提高晶振的精度。采用高质量晶片:选择品质优良的石英晶片作为原材料,确保晶振具有更好的物理性能和稳定性。采用先进的封装技术:选择适当的封装材料和封装方式,以减少外部环境对晶振的影响,提高稳定性。同时,一些封装技术还设计了温度补偿机制,能够进一步提高晶振的精度。优化电路设计:在晶振的电路设计中,采用线性电源或低噪声电源,加入滤波电容以减少电源噪声。同时,优化PCB布局布线,减小寄生电感电容的影响。外部干扰防护:采取屏蔽措施以减少外部电磁干扰对晶振的影响。例如,使用金属罩来保护晶振,或者采购抗干扰能力更强的差分晶振。精确匹配电容:精细无误的电容匹配能让晶振发挥出更稳定的功效。在选取电容时,要尽可能选用精度高的电容器,并且尽量选用数值一样的电容器,以避免使用误差大的电容器导致晶振频率产生偏差。通过以上措施,可以有效提高晶振的精度和稳定性。单片机晶振必要性探讨,单片机晶振常见问题分析。晶振tcx

晶振的谐振频率是如何确定的?iqd晶振

晶振的启动时间是指从通电到晶振开始稳定振荡所需的时间,这个时间一般很短,通常在几毫秒到几秒之间,取决于晶振的类型、频率和外部电路等因素。晶振的启动时间对电路启动有重要影响。在一些对实时性要求较高的应用中,电路需要在短时间内启动并开始工作,因此晶振的启动时间必须足够短,以确保电路能够迅速进入正常工作状态。如果晶振的启动时间过长,可能会导致电路启动失败或无法满足实时性要求。此外,晶振的启动时间还与电路的稳定性有关。如果晶振在启动过程中受到干扰或发生故障,可能会导致电路无法正常工作或产生不稳定的现象。因此,在选择晶振时,需要考虑其启动时间以及稳定性等参数,以确保电路能够稳定可靠地工作。在实际应用中,为了降低晶振的启动时间并提高电路的稳定性,可以采取一些措施,如优化电路设计、选择合适的晶振类型和频率、调整外部电路参数等。这些措施有助于提高电路的性能和可靠性,使其能够满足各种应用需求。iqd晶振